Virginia Semiconductor Inc since 1997

Virginia Semiconductor

The smart choice for your semiconductor needs

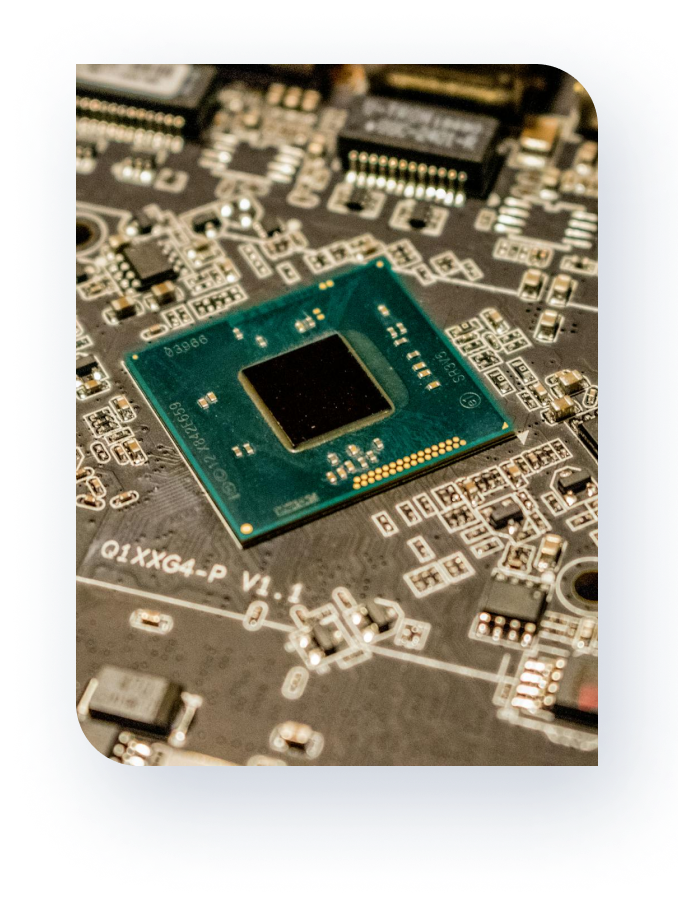

About Virginia Semiconductors

Virginia Semiconductor is a fully integrated custom silicon wafer manufacturer serving customers across the world. Our silicon wafers are made from scratch making it easy to repeat specifications from batch to batch and quickly fix any issues that occur.

Find The Product You're Looking For

Virginia Semiconductor is a fully integrated custom silicon wafer manufacturer serving customers across the world. Our silicon wafers are made from scratch making it easy to repeat specifications from batch to batch and quickly fix any issues that occur.

Our 3 Core Expertise

Virginia Semiconductor is the Worlds #1 online source for Silicon Wafers and Substrates since 1997.

Silicon Wafers

Virginia Semiconductor carries both Single Side Polished (SSP) and Double Side Polished (DSP) wafers available in stock. These wafers range from one to six inches in diameter with other specifications available.

Silicon Ingots

In addition to the common products and sizes, we can make any silicon wafer to any specification, including small, complicated orders. This includes crystal growth, grinding, slicing, lapping, polishing, oxidation, and SOl.

Integrated Circuits

We are a leading manufacturer of prime silicon substrates, offering production quantities of 1-150mm diameter silicon and small quantities of custom silicon substrates. We also offer SOl substrates that range from 25.4mm to 150mm.

F.A.Q's

We produce a variety of silicon wafers tailored for different applications, including semiconductor-grade wafers, solar wafers, and specialized wafers for MEMS, sensors, and optical applications.

Yes, we specialize in custom wafers and can adjust thickness, diameter, resistivity, and other parameters to meet your unique project requirements.

Lead times vary based on the complexity and specifications of the order. Standard orders typically take 4–6 weeks, while more customized orders may take longer. Please contact us for a detailed estimate.

- Absolutely. We provide both n-type and p-type doped silicon wafers and can adjust the resistivity according to your needs. Contact us to discuss your specific requirements.

We offer a range of sizes from 2-inch to 12-inch wafers. For custom sizes, please reach out, and we’ll work to accommodate your specifications.

We'd love to hear from you

Stay Connected

LEAVE A REQUEST FOR A CONSULTATION TODAY!

Reach us through

- 1501 Powhatan Street in Fredericksburg, Virginia USA

- 540.373.2900

- info@viginiasemiconductors.com